Avtomatska optična postaja za predelavo BGA

Pogosto se uporablja pri popravilih na ravni čipov za matične plošče mobilnih naprav, prenosnih računalnikov, računalnikov, televizorjev, klimatskih naprav itd. Ima visoko uspešnost popravil in visoko stopnjo avtomatizacije ter prihrani veliko človeških naporov. Smo profesionalni proizvajalec tega stroja in ga imamo na zalogi.

Opis

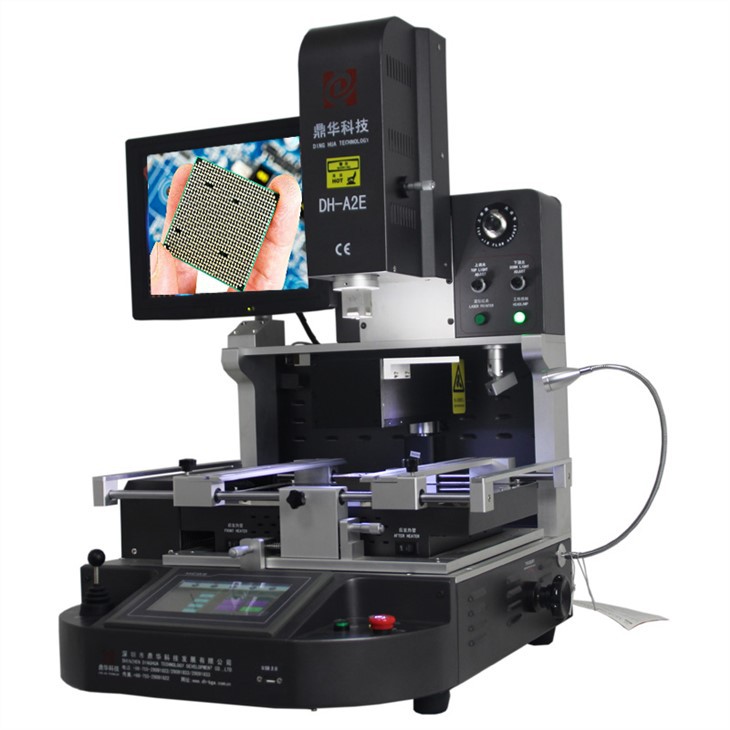

Avtomatska optična postaja za predelavo BGA

1. Uporaba avtomatske optične postaje za predelavo BGA

Matična plošča računalnika, pametnega telefona, prenosnika, MacBook logične plošče, digitalnega fotoaparata, klimatske naprave, TV-ja in druge elektronske opreme

oprema iz medicinske industrije, komunikacijske industrije, avtomobilske industrije itd.

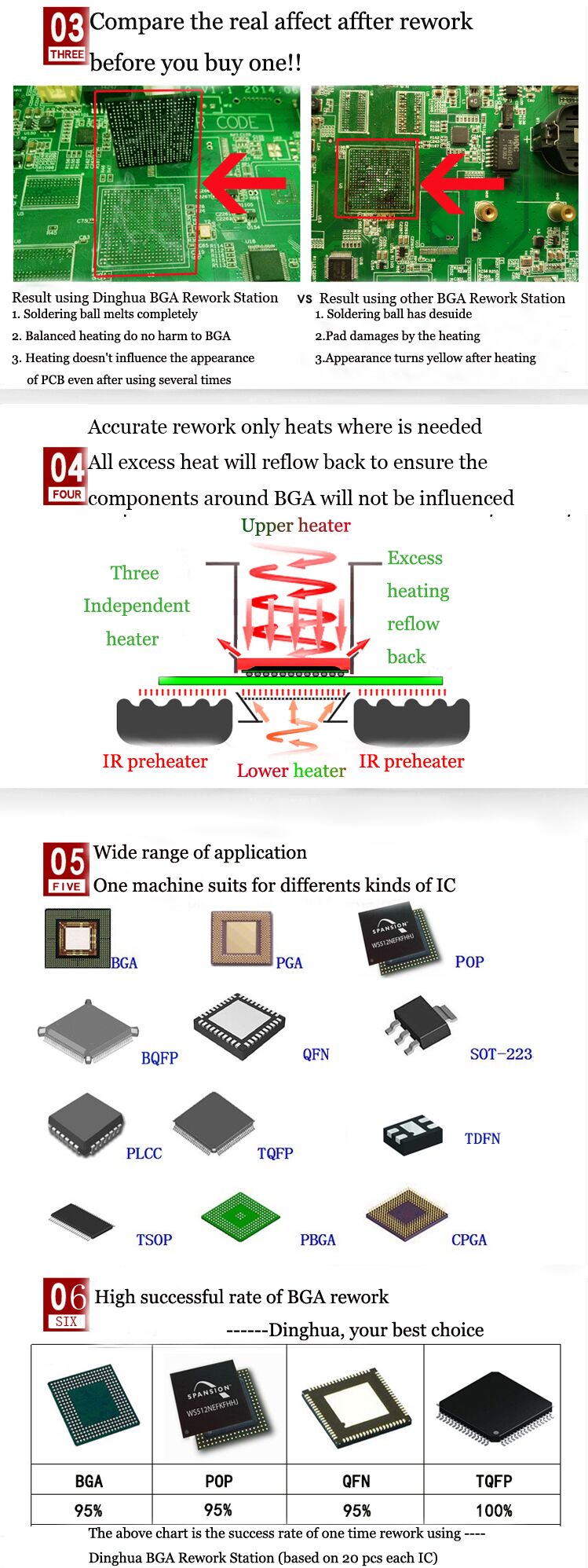

Primerno za različne vrste čipov: BGA, PGA, POP, BQFP, QFN, SOT223, PLCC, TQFP, TDFN, TSOP, PBGA, CPGA, LED čip.

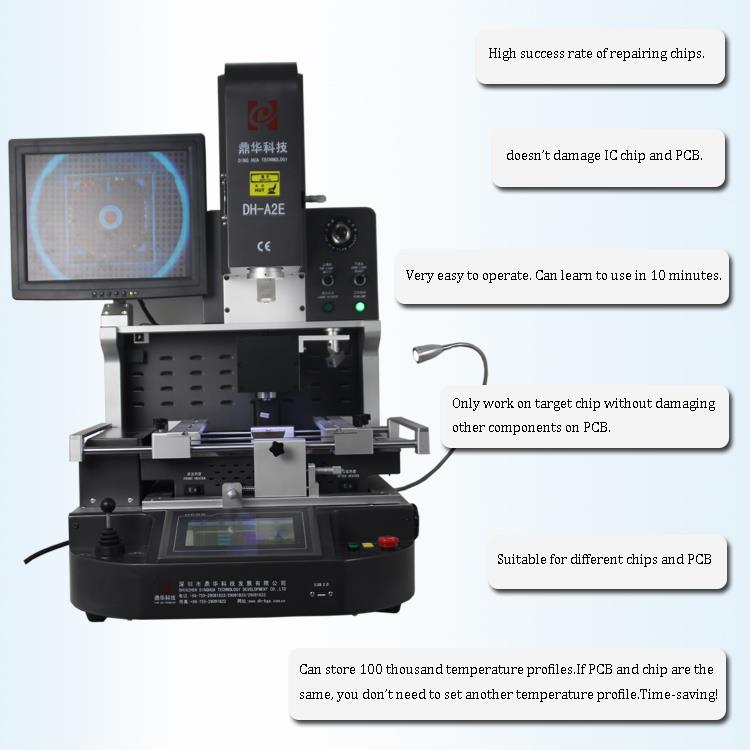

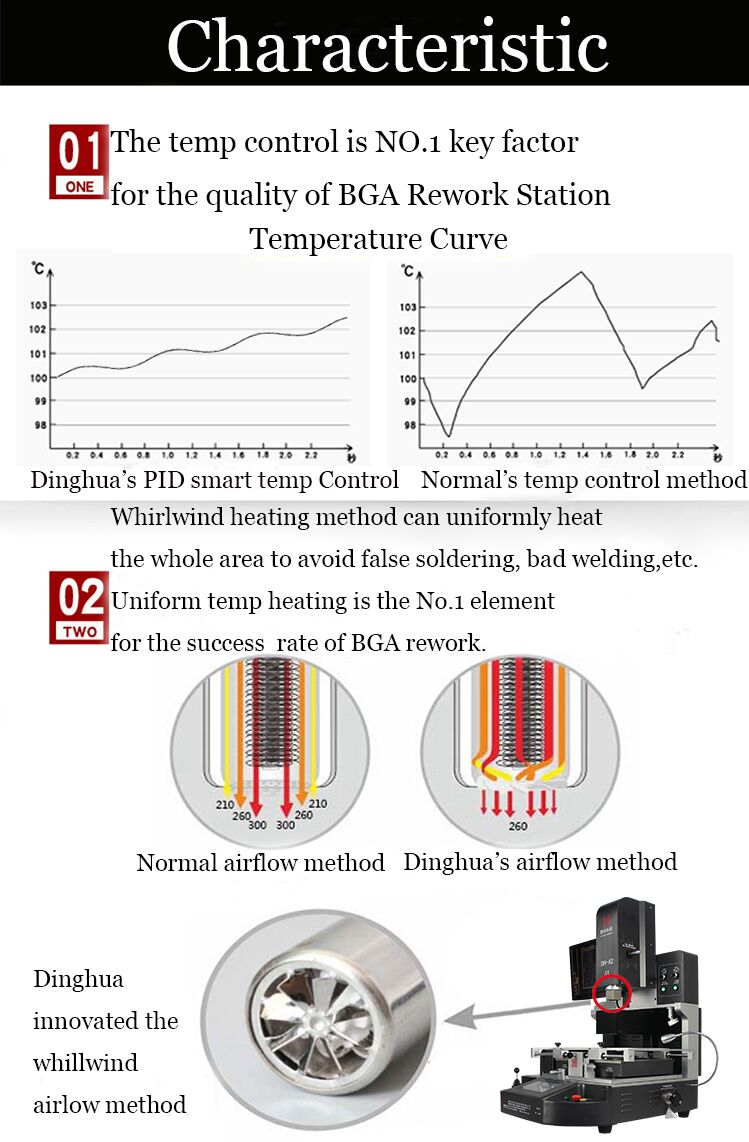

2. Lastnosti izdelka Auto Optical BGA Rework Station

• Visoka stopnja uspešnosti popravil na ravni odrezkov. Odspajkanje, montaža in spajkanje poteka samodejno.

• Natančno poravnavo vsakega spajkalnega spoja je mogoče zagotoviti s CCD kamero za optično poravnavo.

•Natančen nadzor temperature je mogoče zagotoviti s 3 neodvisnimi ogrevalnimi področji. Stroj lahko nastavi in shrani

1 milijon temperaturnega profila.

• Vgrajeni vakuum v montažni glavi samodejno pobere BGA čip po končanem odspjkanju.

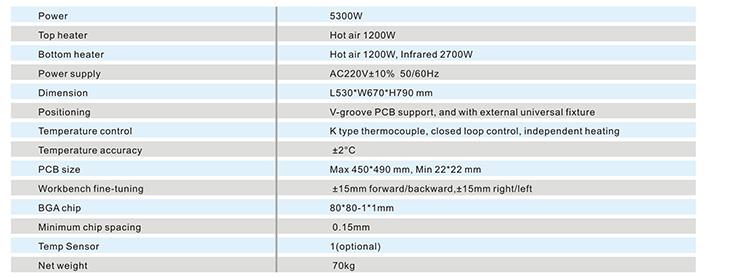

3.Specifikacija avtomatske optične postaje za predelavo BGA

4. Podrobnosti o avtomatski optični postaji za predelavo BGA

CCD kamera (sistem za natančno optično poravnavo); 2. HD digitalni zaslon; 3. Mikrometer (nastavitev kota odrezka);

4.3 neodvisni grelci (toplozračni in infrardeči); 5. Lasersko pozicioniranje; 6. HD vmesnik zaslona na dotik, krmiljenje PLC;

7.Led žaromet; 8. Upravljanje krmilne palice.

5. Zakaj izbrati našo avtomatsko optično postajo za predelavo BGA?

6. Certifikat avtomatske optične postaje za predelavo BGA

7. Pakiranje in pošiljanje avtomatske optične postaje za predelavo BGA

8.FAQ

Kako testirati čip?

Začetni test čipa na sistemski ravni

SoC temelji na globokih submikronskih procesih, zato testiranje novih naprav Soc zahteva popolnoma nov pristop. Ker vsaka funkcionalna komponenta

ima lastne zahteve glede testiranja, mora načrtovalec narediti načrt testiranja zgodaj v procesu načrtovanja.

Izvajati je treba testni načrt blok za blokom za naprave SoC: pravilno konfigurirana orodja ATPG za logično testiranje; kratki testni časi; nove visoke hitrosti

modeli napak in testi več pomnilnikov ali majhnih nizov. Za proizvodno linijo diagnostična metoda ne samo najde napako, ampak jo tudi loči

okvarjeno vozlišče iz delujočega vozlišča. Poleg tega je treba uporabiti tehnike testnega multipleksiranja, kadar koli je to mogoče, da se prihrani čas testiranja. Na področju visoko

integrirano preizkušanje IC, preizkušljive načrtovalske tehnike ATPG in IDDQ imajo močan mehanizem za ločevanje napak.

Drugi dejanski parametri, ki jih je treba načrtovati vnaprej, vključujejo število zatičev, ki jih je treba skenirati, in količino pomnilnika na koncu vsakega zatiča.

Mejni pregledi so lahko vdelani v SoC, vendar niso omejeni na preskuse povezav na ploščah ali modulih z več čipi.

Čeprav se velikost čipa zmanjšuje, lahko čip še vedno zapakira na milijone do 100 milijonov tranzistorjev, število testnih načinov pa se je povečalo na neprimerljivo

ravni, kar povzroči daljše preskusne cikle. To težavo je mogoče preizkusiti. Način stiskanja za rešitev, kompresijsko razmerje lahko doseže 20 do 60 odstotkov. Za današnjo obsežnost

načrtovanje čipa, da bi se izognili težavam z zmogljivostjo, je treba najti testno programsko opremo, ki lahko deluje v 64-bitnih operacijskih sistemih.

Poleg tega se preskusna programska oprema sooča z novimi težavami pri testiranju, ki jih povzročajo globoki podmikronski procesi in naraščajoča frekvenca. V preteklosti je bil testni način ATPG za

testiranje napak statičnega blokiranja ni bilo več uporabno. Dodajanje funkcionalnih vzorcev tradicionalnim orodjem je otežilo iskanje novih napak. Boljši pristop je, da

razvrstite pretekle skupine funkcijskih načinov, da ugotovite, katerih napak ni mogoče zaznati, in nato ustvarite način ATPG, da zajamete te manjkajoče vrste napak.

Ko se načrtna zmogljivost poveča in se preskusni čas na tranzistor zmanjša, se za iskanje težav, povezanih s hitrostjo, in preverjanje časovnega razporeda vezja uporablja sinhrona preskusna metoda

mora biti zaposlen. Sinhrono testiranje mora vključevati več modelov napak, vključno s prehodnimi modeli, zakasnitvami poti in IDDQ.

Nekatera podjetja v panogi menijo, da je lahko kombinacija blokiranja, funkcionalnih in prehodnih/zakasnitve poti najučinkovitejša strategija testiranja. Za globoko

submikronskih čipov in visokofrekvenčnega delovanja, testiranje prehodnosti in zakasnitve poti je še pomembnejše.

Da bi rešili problem natančnosti ATE pri sinhronizaciji testnega jedra in zmanjšali stroške, je treba najti novo metodo, ki poenostavlja vmesnik

preskusna naprava (preizkus prehodnosti in zakasnitve poti zahteva natančno uro na vmesniku preskusne naprave), Zagotavlja, da je signal med preskusom dovolj natančen.

Ker obstaja velika možnost proizvodnih napak v pomnilniškem bloku SoC, mora imeti pomnilniški BIST diagnostično funkcijo. Ko je težava najdena,

okvarjeno naslovno enoto je mogoče preslikati v redundantni pomnilnik rezervne naslovne enote in zaznan naslov napake bo zavržen. Izogibajte se zavrženju

celoten drag čip.

Preizkušanje majhnih vgrajenih pomnilniških blokov odpravlja potrebo po dodatnih vratih ali krmilni logiki. Na primer, tehnike testiranja vektorske pretvorbe lahko pretvorijo

funkcionalne načine v vrsto načinov skeniranja.

Za razliko od metode BIST funkcionalni vnos obvodnega pomnilniškega bloka ne zahteva dodatne logike. Ker ni potrebna dodatna preskusna logika, SoC

razvojni inženirji lahko ponovno uporabijo testne vzorce, ki so bili oblikovani v preteklosti.

Napredna orodja ATPG ne samo vzporedno preizkušajo makre, ampak tudi ugotavljajo, ali obstajajo spori, ter podrobno opisujejo, katere makre je mogoče preizkušati vzporedno in katere

makrov ni mogoče testirati vzporedno. Poleg tega je mogoče te makre učinkovito preizkusiti, tudi če je ura makra enaka uri skeniranja (kot je sinhroni pomnilnik).

Trenutno na gosti dvostranski plošči ni dovolj preskusnih točk in vsak kompleksen čip mora biti opremljen z vezjem za skeniranje robov. brez

skeniranje robov, iskanje proizvodnih napak na ravni plošče je precej težko in ga sploh ni mogoče najti. Z mejnim skeniranjem je testiranje na ravni plošče izjemno enostavno

in neodvisen od logičnega vezja znotraj čipa. Mejno skeniranje lahko tudi konfigurira način ATPG za verigo skeniranja čipa na kateri koli stopnji proizvodnje.